hi3521 watchdog

更新記錄

| item | note |

|---|---|

| 20150916 | 第一版 |

目錄

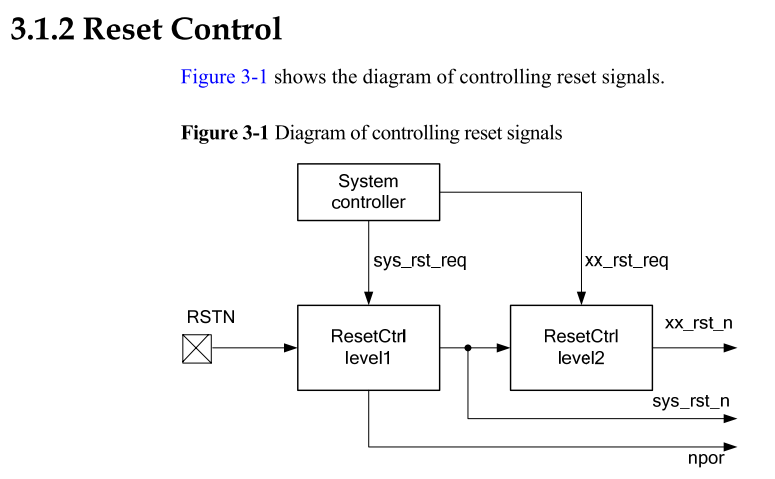

Reset Control

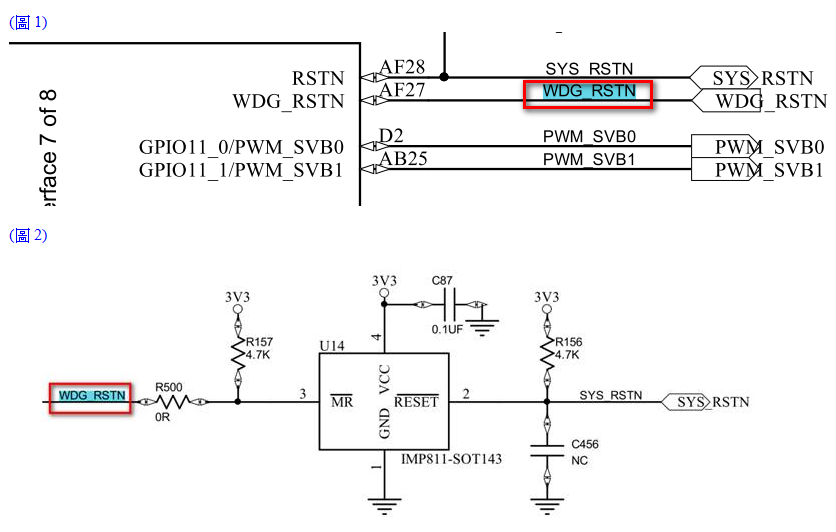

System Pin而言如下

- RSTN Pin: Reset input during system power-on, active low

- WDG_RSTN Pin: WatchDog reset, active low and OD output

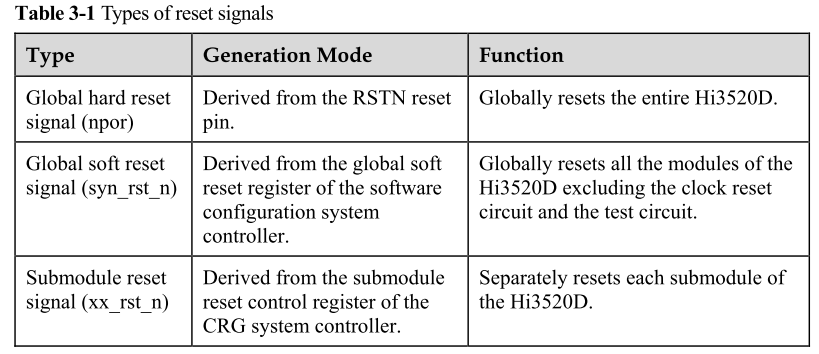

Reset Signal

- RSTN(外部PIN):

- 由外部硬体控制,當Low時Chip進入Power-On Reset

- 由ResetCtrl level1控制產生npor/sys_rst_n/xx_rst_n重置訊號

- sys_rst_req(內部regsiter):

- 由內部暫存器控制

- 當下執指令reboot時,最於就是設定此暫存器來達到重開機

Reset Configuration

- Power-On Reset

the low pulse width of the power-on reset signal is longer than 12 XIN clock cycles.

System Reset 系統重置可由下例2項方式實現

- Power-on reset

- Global soft reset, controll by the system controller

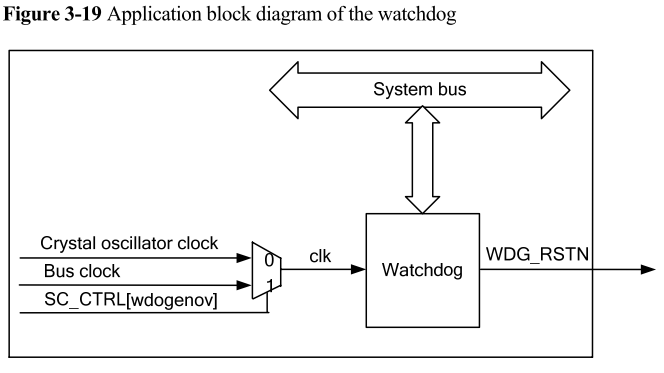

Watch Dog

- 以固定週期reset watch dog counter,當未產生reset counter時將會產生WDT_RSTN訊息

- 配合外部電路達到重置Chip RSTN訊號

- 通常Chip RSTN也會在加上low-power supervisors(IMP811)來防止VCC過低以保護系統穩定度

- 主要目地為系統保護

Watch Dog Block

- SC_CTRL: 選擇Watch Dog的CLK來源

- 內部為32bit counter

實際應用範例

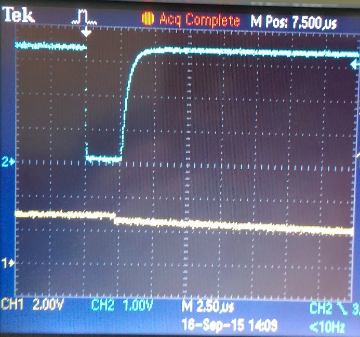

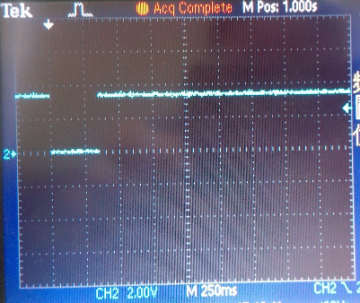

實際量測

- CH2: 為IMP811 PIN3,即WDG_RSTN訊號,產生約2.5us low width

- CH1: 為IMP811 PIN2,即控制CHIP RSTN訊號

- CH2: 為IMP811 PIN2,即控制CHIP RSTN訊號

- 產生約250ms以上的low width

- 以IMP811手冊中說明會最小寬度為140mS

其他說明

- OD output: Ooutput open drain (OD)