了解 i2c原理

更新記錄

| item | note |

|---|---|

| 20160422 | 第一版 |

目錄

I2C

Philips Semiconductors (now NXP Semiconductors) developed a simple bidirectional 2-wire bus for efficient inter-IC control. This bus is called the Inter IC or I2C-bus,ref

features of the I2C-bus

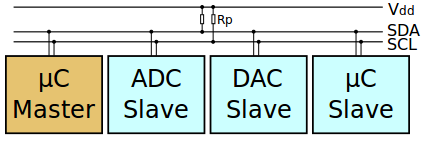

將全部元件由SCL及SDA串接起來,由主控master來決定設定及讀取那個device

Only two bus lines are required; a serial data line (SDA) and a serial clock line (SCL).

Each device connected to the bus is software addressable by a unique address and simple master/slave

每個8bit device address需要唯一 (目前也有10bit address)Serial, 8-bit oriented, bidirectional data transfers can be made at up to 100 kbit/s in the Standard-mode, up to 400 kbit/s in the Fast-mode

UM10204)">I2C-bus specification and user manual(UM10204)

The I2C-bus protocol

- Definition of I2C-bus terminology(術語)

| Term | Description |

|---|---|

| Tramsmitter | the device which sends data to the bus |

| Receiver | the device which receives data frome the bus |

| Master | the device which initiates a transfer,generates clock signals and terminates a transfer |

| Slave | the device addressed byh a master (當master送出start-bit+device address,此時deaddress為slave) |

- Applicability of I2C-bus protocol features

M = mandatory

O = optional

n/a = not applicable

| Feature | Single Master | Mutlti-master | Slave |

|---|---|---|---|

| Start condition | M | M | M |

| Stop condigion | M | M | M |

| Acknowledge | M | M | M |

| Synchronization | n/a | M | n/a |

| Arbitration | n/a | M | n/a |

| 7bit slave address | M | M | M |

| 10bit slave address | O | O | O |

| Device ID | n/a | n/a | O |

最基本的協定:Start condition/Stop condition/ACK/7bit slave address

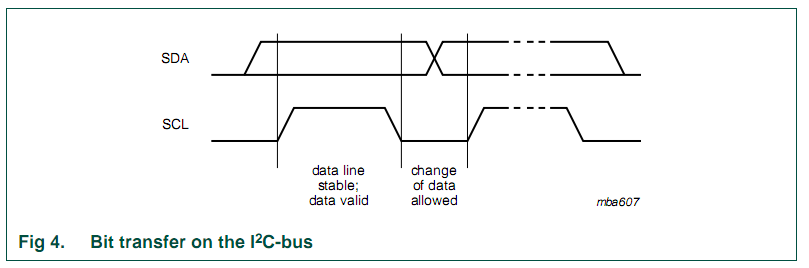

Data validity(何為有效資料)

The data on the SDA line must be stable during the HIGH period of the clock

當Clock(SCL)為High時,此時SDA是不允許被設定,即為stable (此時master會去strob資料/讀取資料)The High or Low state of the data line can only change whe the clock signal on the SCL line is LOW

當Clock(SCL)為LOW時,slave 可以設定資料

[圖片來源:UM10204]

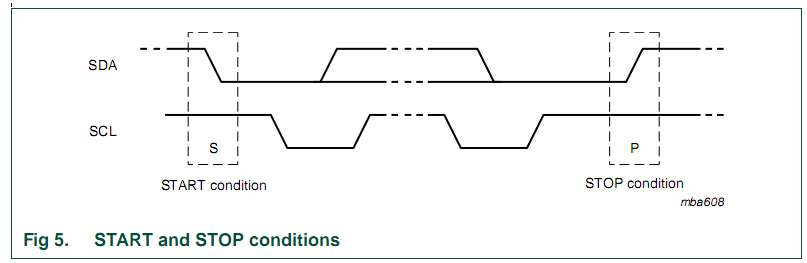

START and STOP condition

START and STOP condition alway generate by the master

the busy is considered to be busy after START condition

the busy stays busy if a repeated START (Sr) is generated instead of a STOP condition.

誰可以在CLK為High去改變SDA?? (只有master去產生start/stop condition)

[圖片來源:UM10204]

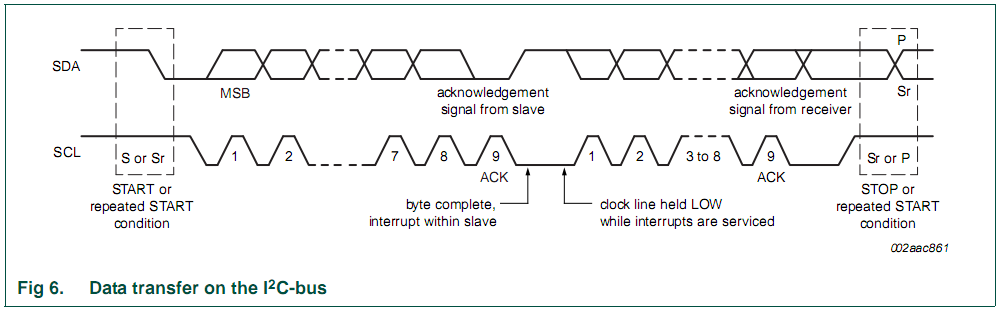

Byte format

Every byte put one the SDA line must be eight bits long.

SDA資料byte,規定為8個bit長度The number of byte that can transmitted per transfer is unrestricted.

無規定每次傳輸有幾個byte,由slave datasheet決定Each byte muste be followed by an Acknowledge bit.

每個byte,需再接受ACK訊號(1個bit),一共9個bit資料Data is transferred with Most Significant Bit(MSB)

高元位先傳送for example servicing an internal interrupt, it can hold the clock line SCL LOW to force the master into a wait state.

- 注意在傳送完1byre frame之後,可以將clk設定為low,接著CPU可以去處理中斷事情,在回來續傳

[圖片來源:UM10204]