工作上遇到網路不通(即PHY not link),了解一下整個流程

在ISO 7層中的physical,即為目前phy chip(RTL8211EG)

使用MII介面串接到SOC,因此在SOC裡會有MAC程式

更新記錄

| item | note |

|---|---|

| 20160617 | 第一版 |

目錄

基本原理了解

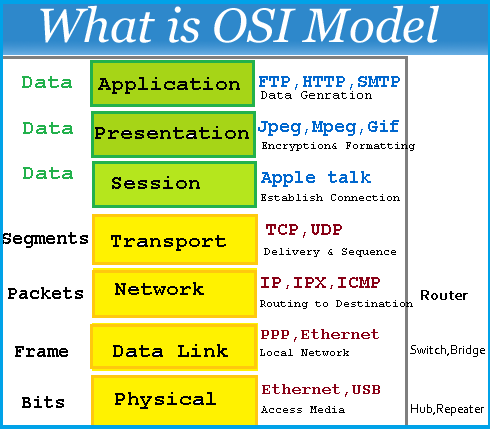

OSI model

寫driver至少要了解最底層兩層 physical & data link layer

-

OSI Model(Open System Interconnetion Model)

一共有7層如上圖所示,IEEE 802定義data link及physical的關系

Physical Layer

- 主要為硬体部分,ex Repeater,hub

- 將底層的bit料層送到data link layer

- 定義硬体的電性規格(ex. timing, voltage) 、佈線方式(topology)等

Data link Layer

- IEEE 802規格將此層分為LLC(802.2)與MAC(802.3,802.4等)

- encode the bit into packet and edcode the packet into bit

- Its provide error free transfer the frame one node to another node.

- function of the Data Link Layter

- Logical Link Control

- Data Framing

- Hardware Addresing

- Error detection and Handling

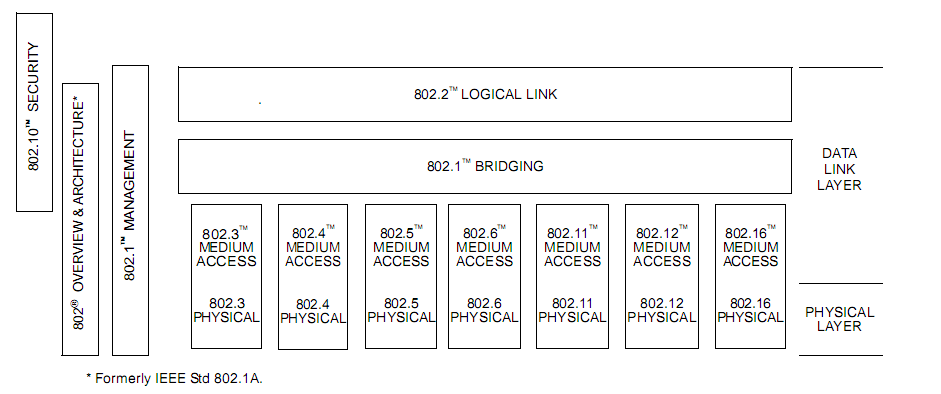

IEEE STD 802

| Name | Description |

|---|---|

| IEEE 802.1 | Higher Layer LAN Protocols |

| IEEE 802.2 | LLC (Logical Link control) |

| IEEE 802.3 | Ethernet |

| IEEE 802.4 | Token bus |

| IEEE 802.11 | Wirless LAN(WLAN) |

- IEEE Standard for Local and Metropolitan Area Networks

- IEEE 802定義 lower two layer(Data Link and Physical)協定及規格

- 定義physical Layer 及 data link layer相關

- IEEE 802將Data Link Layer分成兩部分:

- LLC Sublayer

- Mac Sublayer

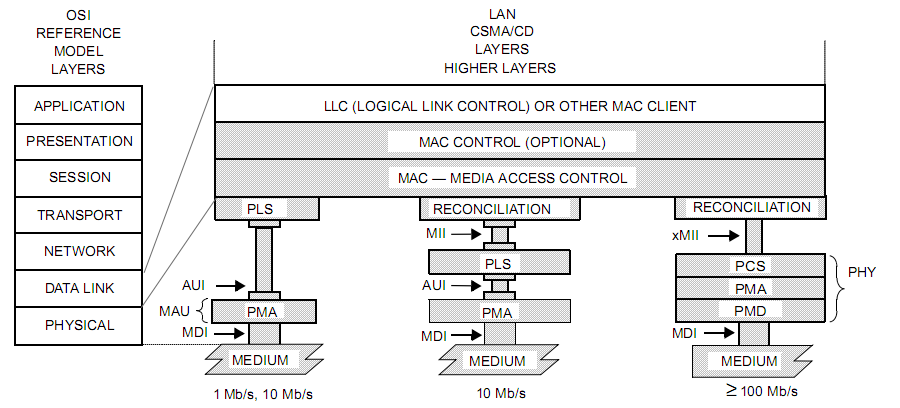

CSMA/CD

- 來源-Ethernet]

- 每個網路設備都有一個唯一的MAC(medium access control)

- 此mac都常是記錄在網路卡NIC(network interface card)裡面的ROM

- 來源-IEEE 802.3 CSMA/CD網路

- Carrier Sensing Multiple Access with Collistion Detection

- IEEE 802.3標準制定了CSMA/CD

- 通訊協定採用 CSMA/CD,沒有提供優先權傳輸服務

- 訊框格式為 IEEE 802.3 CSMA/CD 訊框

PHY重要的功能就是實現CSMA/CD的部分功能

- 它可以檢測到網路上是否有數據在傳送,如果有數據在傳送中就等待

- 一旦檢測到網路空閑,再等待一個隨機時間后將送數據出去

IEEE 802.3 CSMA/CD 訊框

| size | item |

|---|---|

| 7 | Preamble |

| 1 | SOF(Start-of-Frame DElimiter) |

| 6 | Destiantion Address |

| 6 | Source Address |

| 2 | Length |

| 46-15000 | 802.2 Header and Data |

| 4 | FCS (Frame Check Sequence) |

IEEE 802.3 Standard relationship

- 出處-IEEE Standard for Ethernet.pdf(IEEE Std 802.3-2012) page 3

| Interface | Description |

|---|---|

| PHY | physical layer device (由PCS,PMA,PMD組成) |

| PCS physical conding sublayer | |

| PMA physical medium attachment | |

| PMD physical medium dependnet | |

| MII | medium independent interafce |

| MII for 100BASE-T | |

| AUI | attachment unit interface |

| AUI for 10BASE-T | |

| MDI | medium dependent interface |

| xMII | MII for implementation of 100Mb/s and above |

| GMII for 1Gb/s | |

| XGMII for 10Gb/s |

實体介面

- PHY (ex.RTL8211EG IC用來實做PHY)

- INTEGRATED 10/100/1000M ETHERNET TRANSCEIVER

- rtl8211e(g)-vb(vl)-cg_datasheet_1.6.pdf

MII

- 出處-MII,RMII,GMII介面詳細解釋

- 乙太網媒體介面有:MII RMII SMII GMII

- MII是(Medium Independent Interface)的意思,是指不用考慮媒體是銅軸、光纖、電纜等,

- 因為這些媒體處理的相關工作都有PHY或者叫做MAC的晶元完成。

- “媒體獨立”表明在不對MAC硬體重新設計或替換的情況下,任何類型的PHY設備都可以正常工作。

- MII數據介面總共需要16個信號

- MII管理介面是個雙信號介面,一個是時鐘信號,另一個是數據信號。

- PHY裡面的部分寄存器是IEEE定義的,這樣PHY把自己的目前的狀態反映到寄存器裡面

MII /RGMII

- rtl8211e(g)-vb(vl)-cg_datasheet_1.6.pdf

- MII,RGMII

| item | Transmitter | Reciveer |

|---|---|---|

| MII(10Mbps) | transmit 4-bit, TXD[3:0] | 4bit |

| clock: 2.5MHz(TXCLK) | 2.5Mhz | |

| Manchester-encode data stream | ||

| MII(100Mbps) | trasmit 4-bit TX[3:0] | 4bit |

| clock: 25MHz(TXCLK) | 25Mhz | |

| 4B/5B coding technology | ||

| GMII(1000Mbps) | 125Mbaud/s | 8bit |

| 4D-PAM5 coding techology | 125MHz |

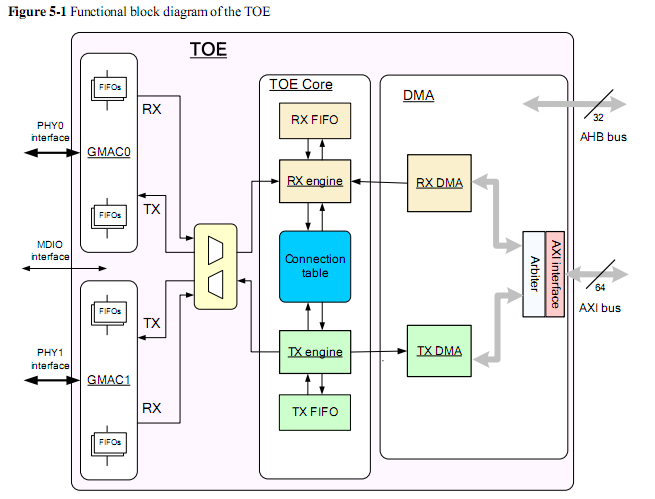

Hi3521 MAC

RMII

- 使用RTL8211EG PHY,通過RMII介面串接到Hi3521

| pin | note |

|---|---|

| TXD[0-3] | MAC to PHY |

| TXEN | Transmit Enable |

| TXCK | transmit clok 2.5MHz or 25MHz |

| TXCKOUT | transmit clock 125MHz |

| RXD[0-3] | PHY to MAC |

| RXDV | receive data vad |

| RX_CK | phy. RXCLK source the 125MHz receive clock |

| MDC | Management Data Clock. |

| MDIO | Input/Output of Management Data. |

| CRS | Carrier Sense (由phy產生) |

| COL | Collision In Half Duplex Mode. |

- the MDC and MDIO pins as described in IEEE 802.3u section 22.

- The MDC signal, provided by the MAC, is the management data clock reference to the MDIO signal

Hi3521 Ethernet Port

gigabit media access control GMAC)

- RGMII or MII mode

- 10/100 Mbit/s full-duplex or half-duplex mode

- 1000 Mbit/s full-duplex mode

- TOE for reducing the CPU usage

- provide a management data input/output (MDIO) interface

GMAC pin

| pin | note |

|---|---|

| RGMII_COL | RGMII-> Collision indicator signal |

| MII -> RGMII_TXER | |

| RGMII_CRS | RGMII -> RGMII_CRS |

| MII -> RGMII_RXER | |

| RGMII_RXCLK | Receive clock for the RGMII or MII |

| RGMII_RXD[0-3] | |

| RGMII_RXDV | |

| RGMII_TXCK | MII -> RGMII_TXCK |

| RGMII_TXCKOUT | RGMII |

| RGMII_TXD[0-3] | |

| RGMII_TXEN | transmit data enable of the RGMII or MII |